参考文献: LD7580R 应用手册及 IC 规格书

## 1. 交错式功率因数修正电路(Interleaved Power Factor Correction)背景说明

交错式功率因数校正 (Interleaved PFC) 是一种将多个功率因子校正级并联运作，并透过相位错开来达成整体效能提升的技术。其发展主要受到高功率应用对体积、效率及电磁干扰 (EMI) 等要求的驱动控制器。因应电源产品发展走向轻薄化在产品内部限制高度变得相对严苛，Interleaved PFC 可将 PFC CHOKE 分成两组降低高度，在高度限制的设计上有相对优势，广泛应用在显示器产品。

## 2. 交错式功率因数修正电路核心优势：

### ▲涟波电流消除：

透过各相位的错开操作，能有效抵消输入电流和输出电容电流的涟波，显着降低电磁干扰 (EMI)，并允许使用更小尺寸的输入/输出电容器及 EMI 滤波器。

### ▲磁性组件缩小：

PFC Choke 由 1 组分成两组，减少了单一电感的储能需求，进而缩小了电感体积。

### ▲功率密度提升：

由于组件体积缩小和热管理改善，整体转换器能达到更高的功率密度。

### ▲热管理改善：

功率耗散分散到多个并联级，有助于更好的散热。

### ▲效率提升：

尤其在高功率应用中，交错式设计能降低导通损耗，提升整体系统效率符合 ESG，达到节能减碳。透过切相 (phase shift management) 技术，也能优化轻载效率。

### ▲组件应力降低：

分散电流负载有助于减少开关组件的电流应力。

### 3. 交错式 PFC 控制器工作模式说明

交错式 PFC 通常由两个或多个升压 (Boost) 转换器并联组成，共同驱动一个直流总线电路。升压转换器因其输入电流连续且易于控制而被广泛用于 PFC 应用。每个并联的升压转换器以固定的相位差独立开关。在双相交错式 PFC 中，两个升压转换器会以 180 度反相的方式运行。由于各阶段的电感电流涟波彼此反相，它们在总输入电流中会部分抵消。这种抵消效应在 50% 的工作周期下最为显着，甚至可将输入电流涟波降至接近零。为了实现精确的电流波形和相位控制，交错式 PFC 需要更复杂的控制电路，可能包含电压环、电流环以及负载平衡控制器，LD7580R 采用数字控制达到成本优化、高度可靠性、提升轻重载效率达到节能减碳，同时也是通嘉科技追求的 ESG 目标，单相与交错式 PFC 比较见表 1。

| 特性                | 单相 PFC            | 交错式 PFC (Interleaved PFC)       |

|-------------------|-------------------|---------------------------------|

| 输入电流涟波            | 较高，需较大 EMI 滤波器    | 显着降低，允许更小的 EMI 滤波器              |

| 输出电容涟波            | 较高，需较大输出电容        | 显着降低，允许更小的输出电容                  |

| 磁性组件体积            | 较大                | 减小，因分散功率并降低涟波                   |

| 功率密度              | 较低                | 较高                              |

| 热管理               | 集中于单一组件，散热压力大     | 功率分散，热管理较佳                      |

| 效率                | 依设计而定             | 整体效率高，轻载效率可透过切相优化               |

| 控制复杂性             | 相对简单              | 较为复杂，但有专用 IC 与数字控制器简化，如 LD7580R |

| 组件数量              | 较少                | 较多，但单一组件 Derating 降低            |

| 适用功率              | 通常适用于中低功率 (<250W) | 适用于中高功率 (<1kW)                  |

| 表 1 单相与交错式 PFC 比较 |                   |                                 |

#### 4. 通嘉交错式 PFC LD7580R 控制器技术特点说明

LD7580R 是一款用于两相交错式功率因子校正器的“数字”IC 控制器，具有  $180^\circ$  相移。由于采用了  $180^\circ$  相移，输入电流涟波显着降低。其专有的电压模式控制算法可实现接近 1 的功率因子，内建补偿功能，并改善总谐波失真 (THD)。LD7580R 具有高度集成，仅需极少的外部组件，采用了  $180^\circ\text{C}$  项移”专利”；以及 COMP 内建”数字”补偿，省去外部的 RC 组件。内建强大的安全保护机制，简化了设计，并确保在高温下可靠运作。

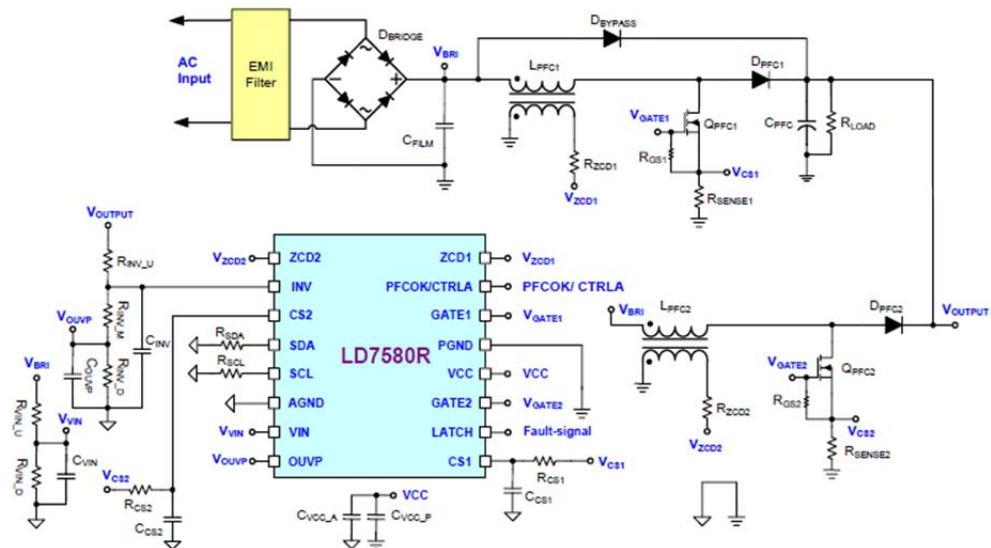

图 1 LD7580R 控制器电路

## 5. LD7580R“数字”式核心 IC 特点

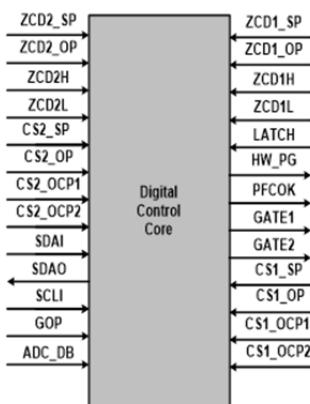

LD7580R 专为交错式升压拓朴功率因子校正而设计的数字 IC。它采用 DCM 工作模式和频率限制方法，并透过 FW 调适方式调整各项关键参数，在所有线路和负载工作范围内实现了高效率、高节能。基于具有 THD 优化功能的电压模式控制算法(Voltage mode control)，LD7580R 可在低线路输入和满载条件下以过渡模式 (CrM) 运行，在高电压输入或轻载条件下以 DCM 模式运行，并具有超低 THD。对于交错式功率因子校正的相移，其内部数字相移控制模式 (Leadtrend 专利) 可在任何线路 / 负载条件下实现 180 度相移。LD7580R 透过 GUI 调整内部参数，在功能灵活性，设计复杂度，精度与可靠性方面皆取代传统模拟 IC 设计上的缺点，实现方式如图 2，数字核心 IC 优势如表 2。

图 2 LD7580R Digital Control Core

## 数字 IC 与仿真 IC 差异比较：

| 特性项目    | 数字 IC 优势                           | 模拟 IC 挑战                            |

|---------|------------------------------------|-------------------------------------|

| 抗噪声能力   | 极强, 信息以离散逻辑状态表示, 不易受干扰。            | 易受噪声影响, 任何干扰都会导致讯号失真。               |

| 精度与可靠性  | 可透过位数增加来任意提高精度, 易于实现错误校正, 产品一致性高。  | 精度受限于组件特性与制程, 易受组件漂移、老化影响, 重复性较差。   |

| 功能灵活性   | 透过软件程序设计实现多种功能, 设计弹性高, 便于功能升级和修改。  | 功能固定由硬件电路决定, 修改功能需重新设计硬件。           |

| 设计复杂度   | 高度模块化, 可利用 EDA 工具自动化设计, 设计效率高。     | 设计复杂, 对组件匹配、寄生效应敏感, 需人工调整优化, 设计时间长。 |

| 集成度与尺寸  | 可高度整合数十亿晶体管, 实现小尺寸、高功能密度。          | 集成度相对较低, 相同功能所需面积较大。                |

| 数据储存与处理 | 易于数据储存、读取和进行复杂运算 (如 DSP), 内存应用广泛。  | 难以直接储存信息, 复杂运算实现困难。                 |

| 成本效益    | 大规模量产时单位成本较低, 因制程标准化且良率高。          | 设计和制造门坎高, 小量生产成本高昂。                 |

| 功耗      | 可透过频率闸控、睡眠模式等技术实现低功耗, 尤其在待机或低速运行时。 | 通常持续消耗功率, 难以实现深度节能模式。               |

表 2 数字 IC 优势

## 6. 通嘉交错式 PFC Controller(LD7580R)技术特点说明

- A. 数字控制器适用于参数设定。

- B. 高功率因子。

- C. 内建 THD 增强器。

- D. 轻载 DCM 模式操作达到高效功能。

- E. 所有条件（包括瞬态条件）下均支持 180° 相移。

- F. CrM/DCM 工作模式。

- G. Driving 能力 Source=700mA, Sink=-1200mA。

- H. Cycle by Cycle Current Limit。

- I. 内建过温度保护(INT. OTP)。

- J. 内建数字补偿，以及轻载关闭一项位，优化效率。

- K. 完善的保护机制。

- 1. 欠压侦测&过压侦测 on VIN pin。

- 2. 过压保护(1st, 2nd OVP) on INV/OVUP pin。

- 3. 欠压保护 on VIN pin。

- 4. 零电流侦测绕组开路&短路保护 on ZCD pin。

- 5. IC GND 开路保护。

- 6. 旁路&升压二极管短路保护。

- 7. LATCH 接脚上的外部锁定功能。

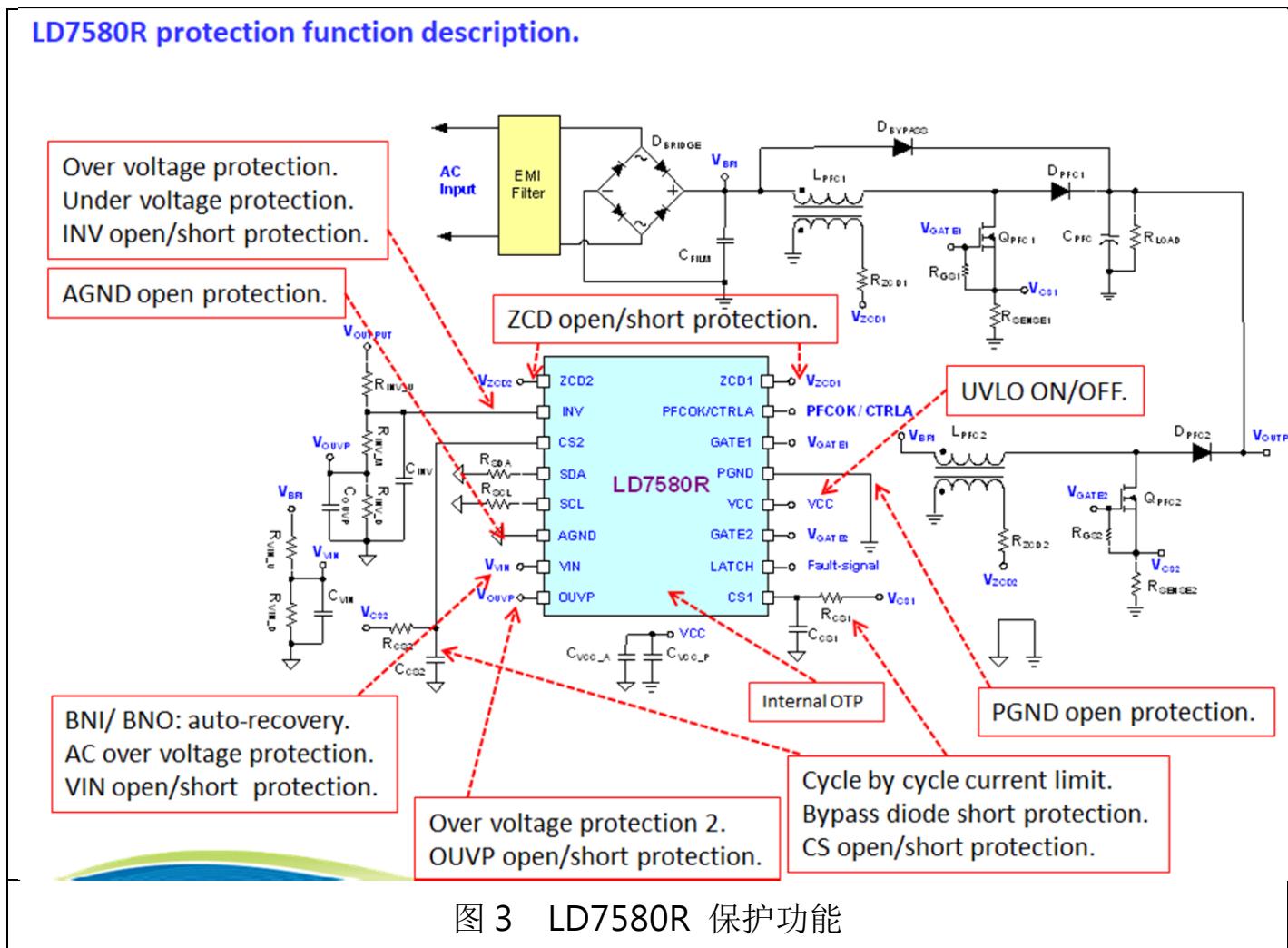

## 7. LD7580R 各 Pin 脚保护功能

LD7580R 针对不同 Pin 脚设置了完整的保护功能，以确保产品的可靠度，以避免在异常状态(来料不良，外部硬力)下造成损伤，针对 PFC 周边组件设置了全面的保护，如：二段式过电压保护，PFC 二极管短路保护，AC 过电压保护，让单一零件失效时，确保产品不会严重损伤，LD7580R 保护功能如图 3，表 3 为仿真单一组件失效，在各种不良条件下 LD7580R 皆进入保护，确保产品的可靠度。

| Item      | 短路后开机 | 开机前短路 |

|-----------|-------|-------|

| PFC 升压二级管 | 无损伤   | 无损伤   |

| Item                                      | 短路后开机            | 开机前短路           |

|-------------------------------------------|------------------|-----------------|

| PFC 电感                                    | 无损伤              | 无损伤             |

| PFC bypass 二级管                            | 无损伤              | 无损伤             |

| 电流取样电阻                                    | 进入 idle mode 无损伤 | 无损伤             |

| INV short to ZCD2<br>(PIN2 short to PIN1) | 触发 OVP2 保护       | 进入 Time Out1 保护 |

| INV short to CS2<br>(PIN2 short to PIN3)  | 触发 CSOP 保护       | 触发 CSOP 保护      |

表 3 单相与交错式 PFC 比较

## 7.1 LD7580R 工作频率说明

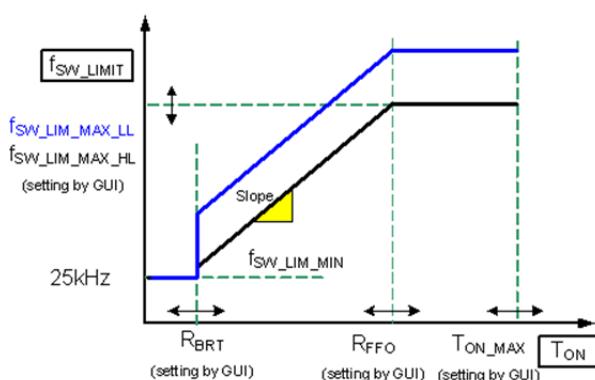

对于 Transition-Mode PFC，开关频率是变动的，并且随着负载的减少，电感放电时间速度快，导通时间固定的情况下，工作频率变快。为了在整个输出负载范围内获得良好的效率效能，LD7580R 实施了频率限制曲线，以减少轻负载时高开关频率造成的额外损耗。LD7580R 实现了 GUI 可设定的最大频率限制 (45kHz~300kHz) 功能，以提高输出轻载/输入高电平条件下的效率，进一步完成节能减排目标。开关频率限制降低点 ( $R_{FFO}$ ) 可透过图形用户接口 (GUI) 设定。最小开关频率限制 ( $f_{SW\_LIM\_MIN}$ ) 固定为 25kHz，以避免开关噪声。开关频率限制的斜率定义图 4。

图 4 LD7580R 频率限制曲线

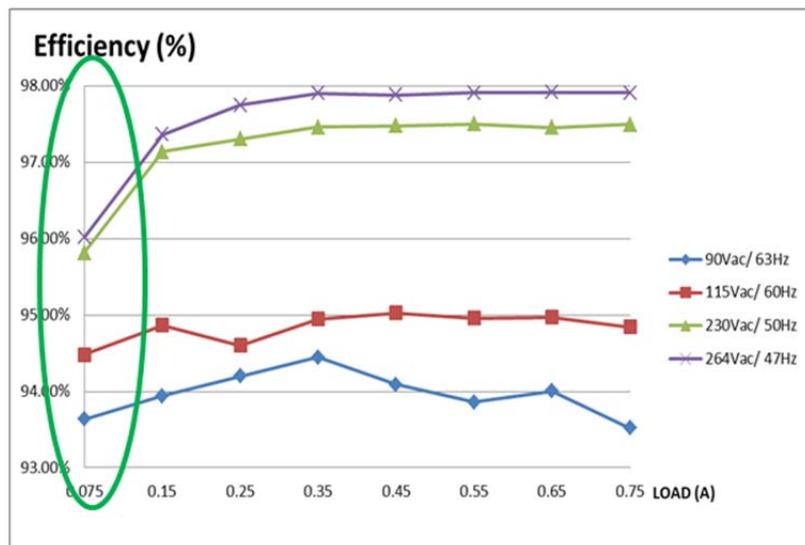

由于频率限制功能，轻载效率显著提升效果如图 5。

图 5 LD7580R 轻载效率优化

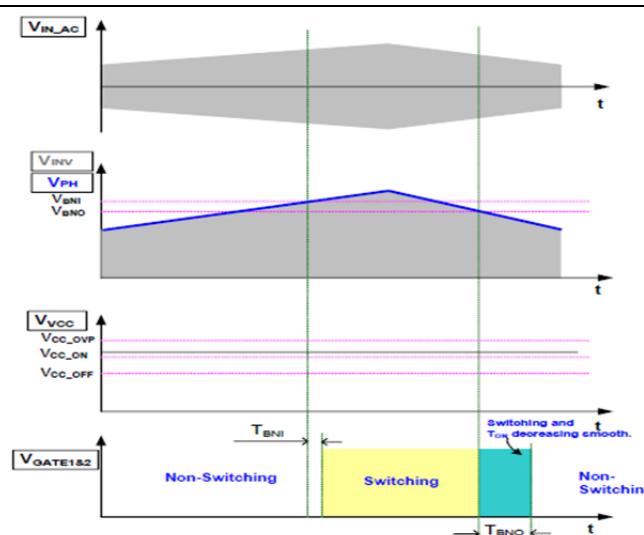

## 7.2 LD7580R 轻载相位关闭说明

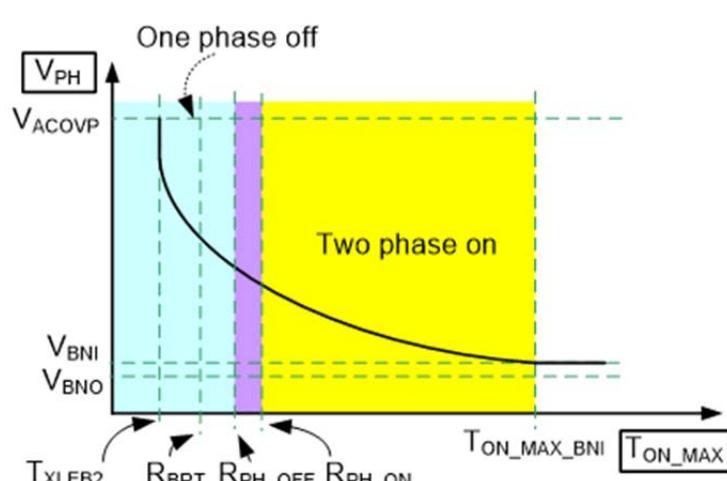

由于轻载条件下切换损失占比大于导通损失，LD7580R 在轻载条件下实现第二相关闭功能”专利”，减少切换损失以提高效率。第二相关闭点 ( $R_{PH\_OFF}$ ) 和第二相开启点 ( $R_{PH\_ON}$ ) 皆可透过 GUI 设定。由于最大导通时间采用非线性前馈补偿，第二相关闭的负载条件在不同的输入电压下均有效。建议  $R_{PH\_OFF} / R_{PH\_ON}$  的值应小于  $40\% * T_{ON\_MAX\_BNI}$ ，达到轻重载效率兼顾。LD7580R 还实现了突发模式阈值电平 ( $R_{BRT}$ ) 的可设定比率，该比率是最大导通时间 ( $T_{ON\_MAX\_BNI}$ ) 的百分比，相位开启关闭说明如图 6。

图 6 LD7580R 相位开启关闭说明

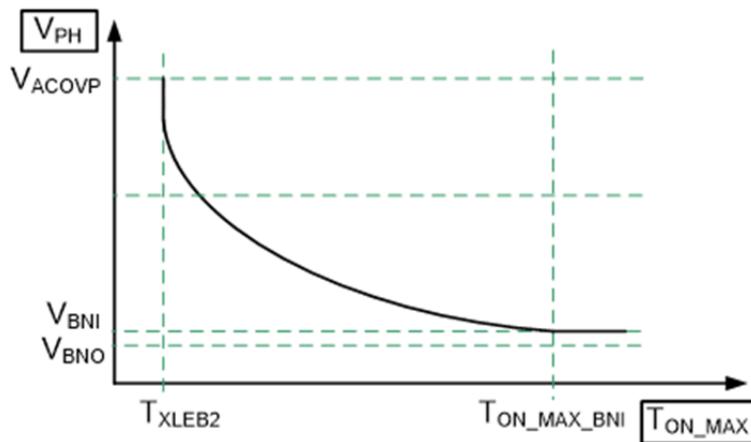

### 7.3 LD7580R 最大导通时间说明

CRM / DCM PFC 最大导通时间由 PFC 电感感量决定, LD7580R 可透过图形用户接口 (GUI) 设定输入电压最低时的最大导通时间 ( $T_{ON\_MAX\_BNI}$ ) (5~40us), 以适应不同的输出功率应用。根据适当的最大导通时间 ( $T_{ON\_MAX\_BNI}$ ) 值, LD7580R 可基于  $V_{PH}$  自动实现非线性前馈补偿, 进而针对不同的输入电压自动调整最大导通时间。最小导通时间 ( $T_{ON\_MIN}$ ) 也可透过 GUI 设定, 范围为  $T_{XLEB2}$  至 0.1\*最小导通时间( $T_{ON\_MAX\_BNI}$ )。

图 7 LD7580R 最大导通时间设定说明

## 7.4 LD7580R 回授功能说明

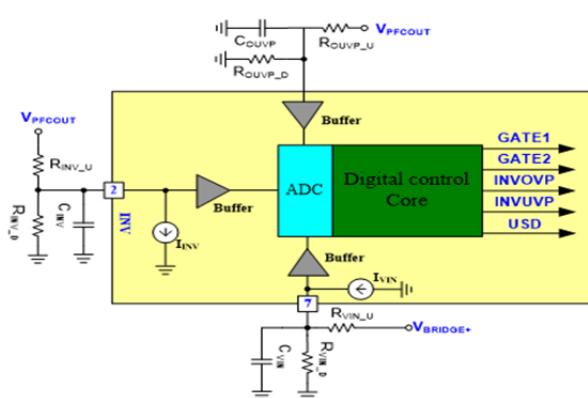

LD7580R 内建数字回馈以调节输出，带宽可在 5~25Hz 范围内设置，相位裕度可透过 GUI 在 45 度至 80 度范围内设定，回馈讯号透过 INV Pin, Vin Pin, OUVP Pin 取样，电路如图 8。

图 8 LD7580R 回授电路

#### 7.4.1 INV Pin 功能说明

INV Pin 借测电解电容电压并藉由电阻  $R_{INV\_U}$  及  $R_{INV\_D}$  进行分压，取样讯号经由 ADC(模拟数字转换器)转换至数字控制达到稳压效果，参考电压(Vref)为 2V，INV 同时设置 1st OVP 功能， INV OVP 参考位准 ROVP 为 108%，设计准则如下：

输出电压对应 Vref 电压公式：

$$V_o = 2V \cdot \left(1 + \frac{R_{INV\_U}}{R_{INV\_V}}\right)(V)$$

设置 Bulk 电压为 395V，可推得  $R_{INV\_U}$  为 6M ohm， $R_{INV\_D}$  为 30.5k ohm。

$$V_o = 2V \cdot \left(1 + \frac{6M}{30.5k}\right) = 395V$$

1st OVP = VREF \* ROVP = 2 \* 108%，可推得 1st OVP 为 427V。

$$V_{oovp} = 2V * 1.08 \cdot \left(1 + \frac{6M}{30.5k}\right) = 427V$$

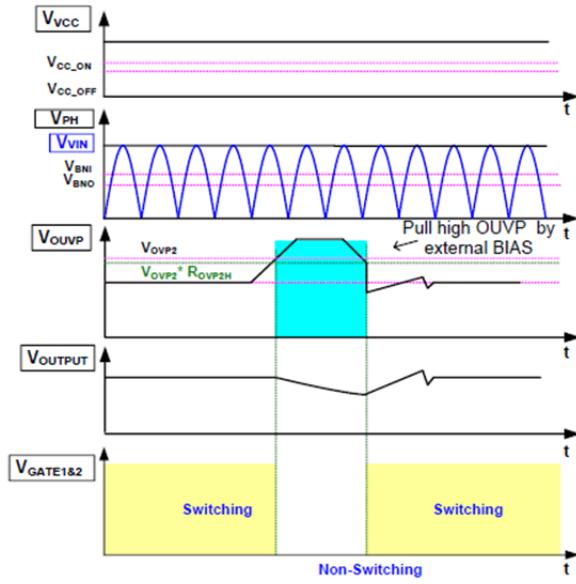

#### 7.4.2 OUVPin 说明

LD7580R 设置了 2nd OVP，增加产品可靠性，可避免当 INV 取样电阻发生异常状态时，可以触发 2nd OVP 以确保不会损伤 Bulk Cap，当 VOUPV 高于 VOVP2 ( $V_{REF}=2V$ )，则触发第二过压保护 (2nd OVP)，LD7580R 将立即关断，直到  $V_{OUVP}$  低于  $V_{OVP2} * R_{OVP2H}$  (97.5%，典型值)，PFC 恢复正常工作，2nd OVP 原理如图 9。

$$V_{oovp} = 2V \cdot \left(1 + \frac{R_{OUVP\_U}}{R_{OUVP\_D}}\right)(V)$$

设置 2nd OVP 电压为 438V，可推得  $R_{INV\_U}$  为 6M ohm， $R_{INV\_D}$  为 27.5k ohm

图 9 OUVP Pin 原理说明

#### 7.4.3 VIN Pin 功能说明

LD7580R 在  $V_{IN}$  引脚上实现了峰值电压保持功能。 $V_{IN}$  引脚的峰值电压 ( $V_{PH}$ ) 用于 Brown in / Brown out。当  $V_{PH} > V_{BNI}$ ,  $V_{GATE1}$  &  $V_{GATE2}$  开始工作, 如图 10 所示。 $VIN$  同时侦测 AC 整流正弦波上升沿, 一旦  $V_{IN} \geq V_{ACOVP}$  (典型值 2.05V),  $ACOVP$  被触发, 对于电力不稳的地区, 有更高的可靠性。LD7580R 提供一个内部恒定源电流  $I_{VIN}$  (典型值 200nA), 用于  $V_{IN}$  接脚开路保护。

图 10 Vin Pin 功能说明

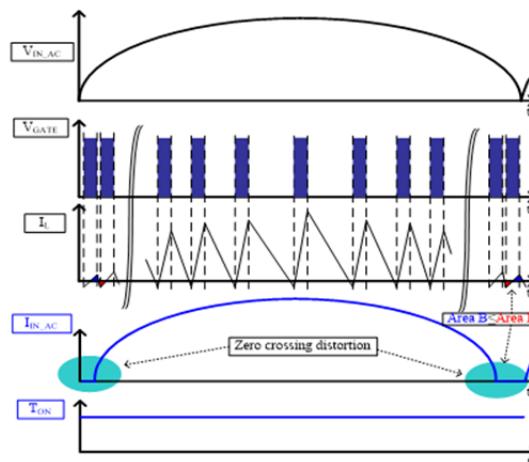

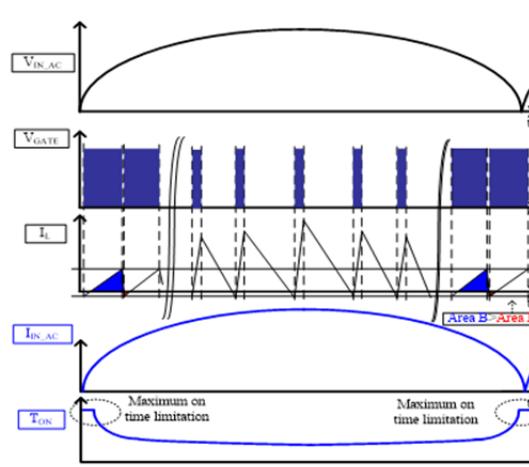

## 7.5 LD7580R THD 补偿功能说明

对于操作模式采用过渡模式 CRM 工作的 PFC Controller, 电感器的负电流是由输入电压的谷底开关引起的。如果输入交流电压接近 0 / 180 度时, 负电流等于或大于电感器的充电电流, 则会发生零点电流失真, 导致总谐波失真 (THD) 增加, 如图 11 所示。

图 11 波谷电流失真示意

当输入交流电压接近 0 / 180 度时, 平滑地增加导通时间可以改善过零失真, 如图 12 所示, LD7580R 工作在 VOT(variable on time)模式下, 以实现低 THD 和高功率因子(PF), 导通时间的变化取决于输入电压、电感器的充电/放电时间和关断时间。

图 12 LD7580R VOT 模式

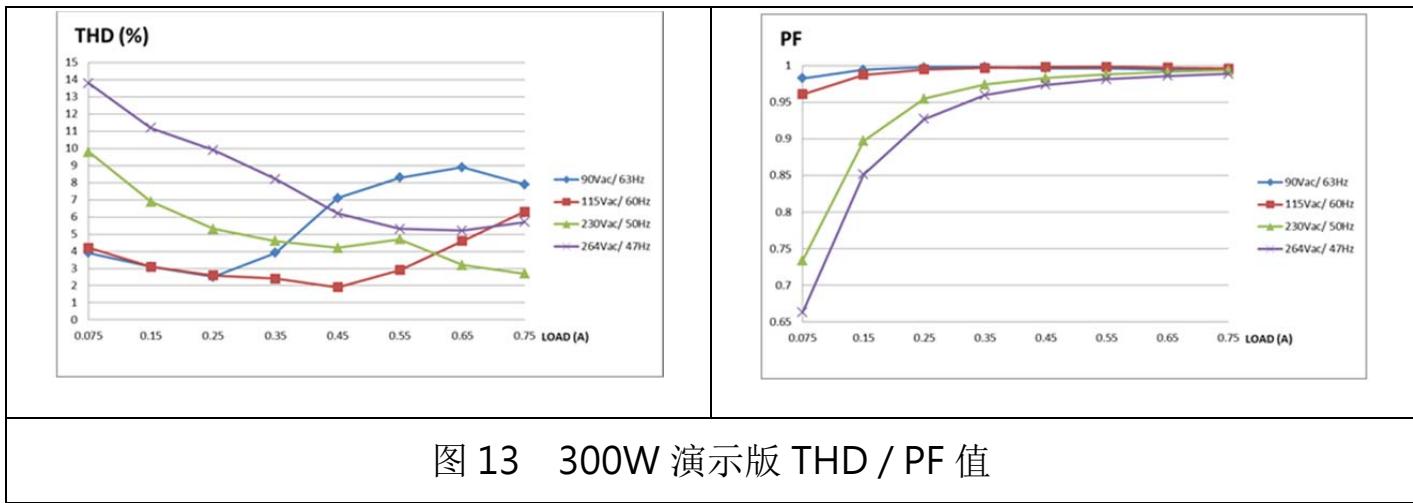

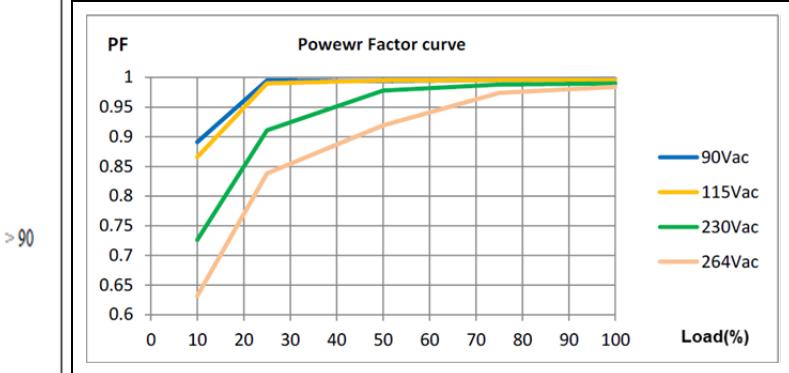

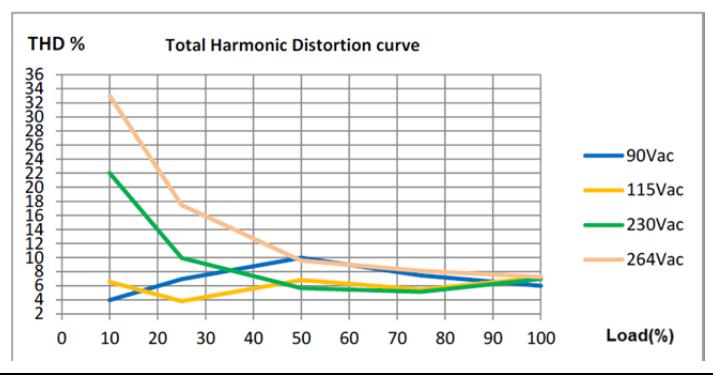

在 300W 的演示版上可以发现不论在轻载或是高电压输入的条件下，LD7580R 实现了低 THD 与高功率因子，如图 13，实现了降低材料成本，并简化设计复杂度，效能表现高于常规 Interleaved PFC IC。

图 13 300W 演示版 THD / PF 值

## 7.6 LD7580R：零电流侦测采用辅助绕组采样

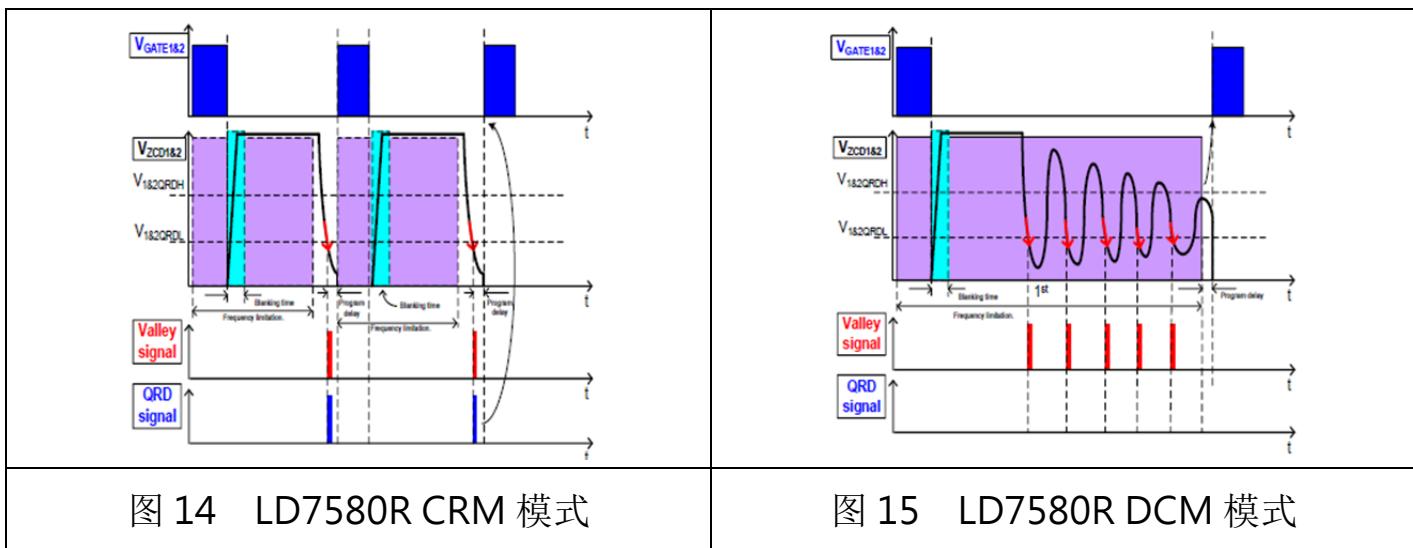

LD7580R 零电流侦测模块( $V_{ZCD1\&2}$ )侦测辅助绕组讯号以驱动 MOSFET。在闸极关断期间，如果  $V_{ZCD1\&2}$  高于  $V_{1\&2QRDH}$  (0.75V, 典型值, 一次电平触发)，则每次低于  $V_{1\&2QRDL}$  (0.25V, 典型值, 下降沿触发) 时，电感电流都会在第一个谷值处闭合为零。根据输出负载条件定义的频率限制，如果谷值讯号出现在频率限制之后，则 LD7580R 工作在 CRM 模式，如图 14 所示。反之，如果频率限制出现在谷值讯号之前，则 LD7580R 工作在 DCM 模式，如图 15 所示，藉由工作模式的切换，进而达到各种负载条件下的效率优化。对于典型应用（输出电压为 390~450V），建议变压器的匝数比约为 10。

图 14 LD7580R CRM 模式

图 15 LD7580R DCM 模式

## 7.6.1 ZCD VCCOK 功能说明

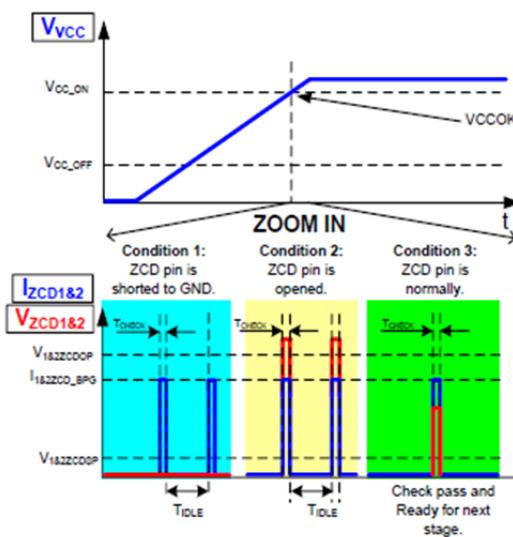

如图 16 所示,  $V_{CCOK} (V_{VCC} \geq V_{CC\_ON}, \text{典型值 } 12.0V)$  后, LD7580R 为  $Z_{CD1}$  和  $Z_{CD2}$  脚位提供两个内部恒定电流源 ( $I_{1\&2ZCD\_PBG}$ , 典型值  $10 \mu A$ ), 以检查焊接状态。如果  $V_{ZCD1\&2}$  高于  $V_{1\&2ZCDOP}$  (典型值  $2.0V$ ), 则触发 ZCD 开路保护 ( $Z_{CDOP}$ ), LD7580R 进入空闲模式, 并在  $T_{IDLE}$  (典型值  $60ms$ ) 后重复检查。如果  $V_{ZCD1\&2}$  低于  $V_{1\&2ZCDSP}$  (典型值  $150mV$ ), 则触发 ZCD 短路保护 ( $Z_{CDSP}$ ), LD7580R 进入空闲模式, 并在  $T_{IDLE}$  后重复进行检查。当  $V_{1\&2ZCDSP} < V_{ZCD1\&2} < V_{1\&2ZCDOP}$  时, ZCD 检查通过, LD7580R 即可进入下一阶段运作。

图 16 VCCOK 功能说明

## 7.6.2 ZCD Time out 功能说明

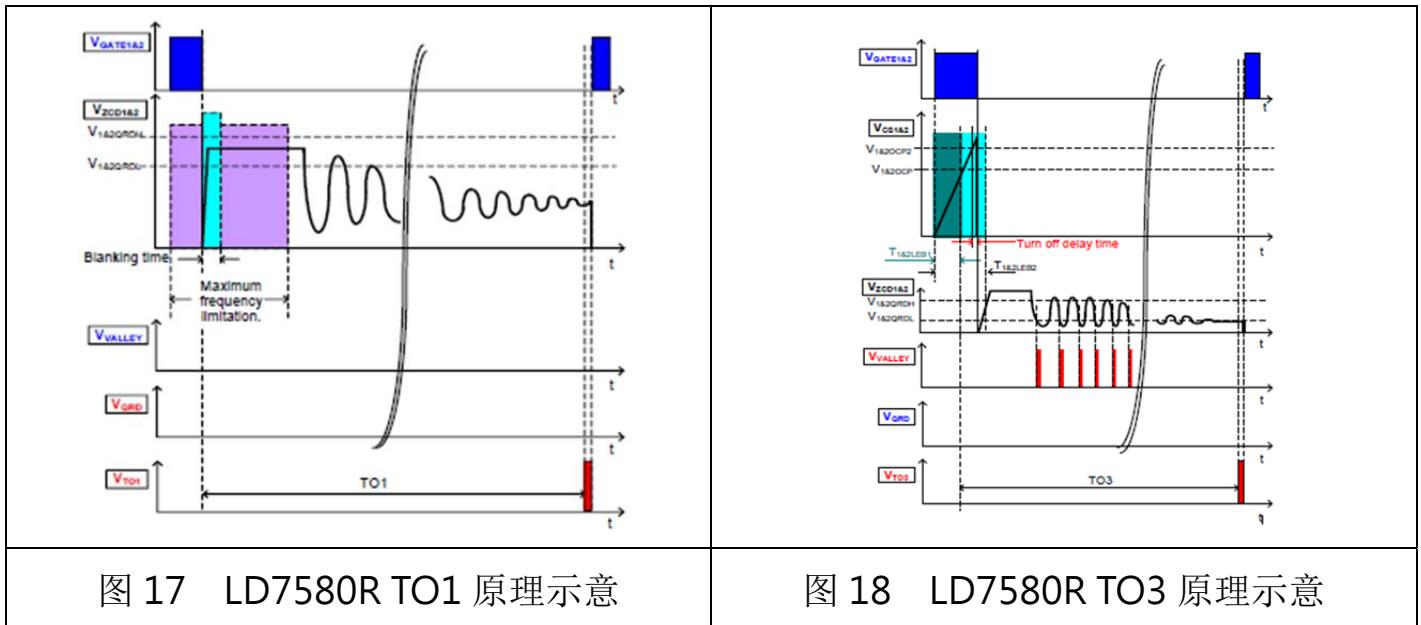

在闸控关闭期间,如果谷底讯号未被触发,则表示  $V_{ZCD1\&2}$  始终低于  $V_1\&V_{2QRDH}$ , Time out 1 功能启动。开关周期限制在  $T_{O1}$  (典型值  $200\ \mu s$ )。如图 17 所示。当  $G_{ATE1\&2}$  脚在  $T_{1\&2LEB1}$  (典型值  $100\text{ns}$ ) 和  $T_{1\&2LEB2}$  (典型值  $200\text{ns}$ ) 之间上升时,一旦  $V_{CS1\&2}$  高于  $V_{1\&2OCP2}$  (典型值  $0.96V$ ), LD7580R 将立即关断,此时已启动保护)。下一个开关周期限制在  $T_{O3}$  (典型值  $800\ \mu s$ ), 以防止损坏。如图 18 所示。

## 7.7 CS Pin 功能说明

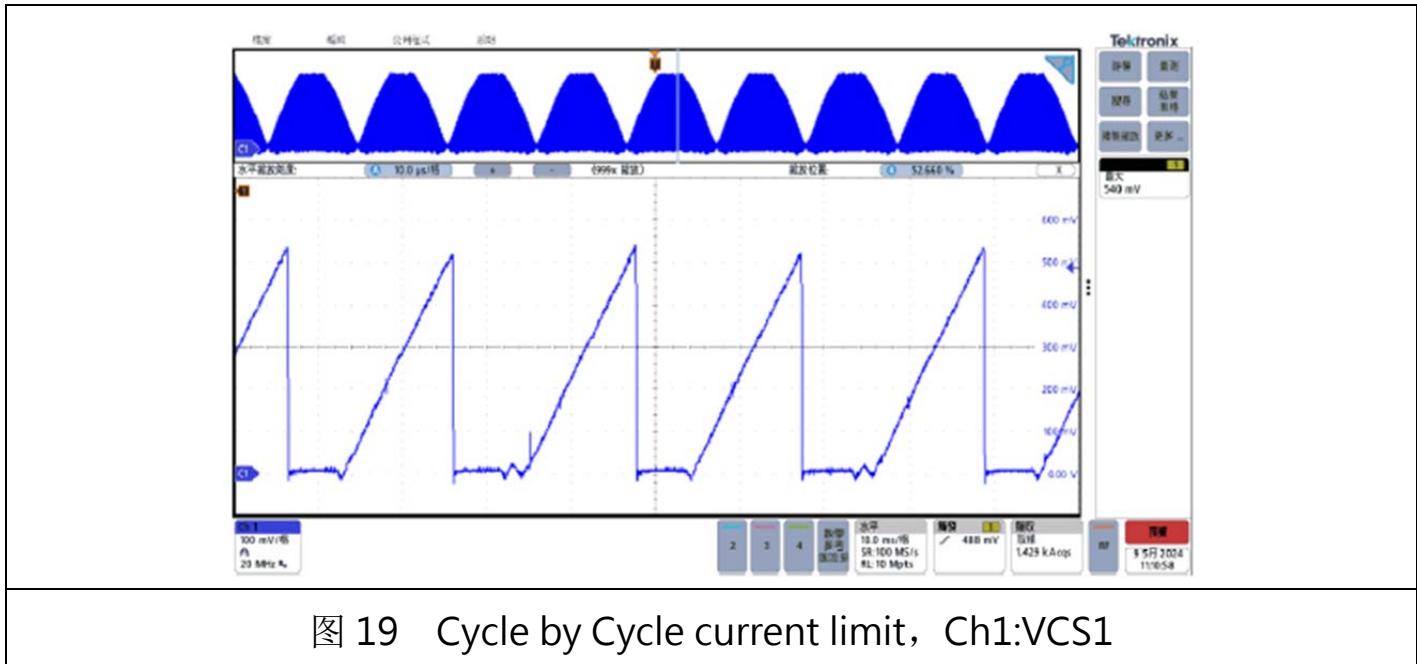

CS 脚位侦测 PFC Mosfet 电流,也就是电感电流,当电流侦测引脚的最大电压阈值设定为  $0.6V$ (透过 GUI 设定),当电压阈值上升至  $0.6V$  将 MOSFET 关断达到 Cycle by Cycle current limit,以防止 PFC 电感饱和,电感饱和计算公式如下,  $Lm$  为 PFC 电感量,  $IL$  为电感电流,  $Np$  为 PFC 电感圈数,  $Ae$  为铁芯截面积, 触发波形如图 19。

$$B_{max} = \frac{Lm * IL}{N_p * Ae}$$

图 19 Cycle by Cycle current limit, Ch1:VCS1

## 7.8 LD7580R 换相(Phase management)说明

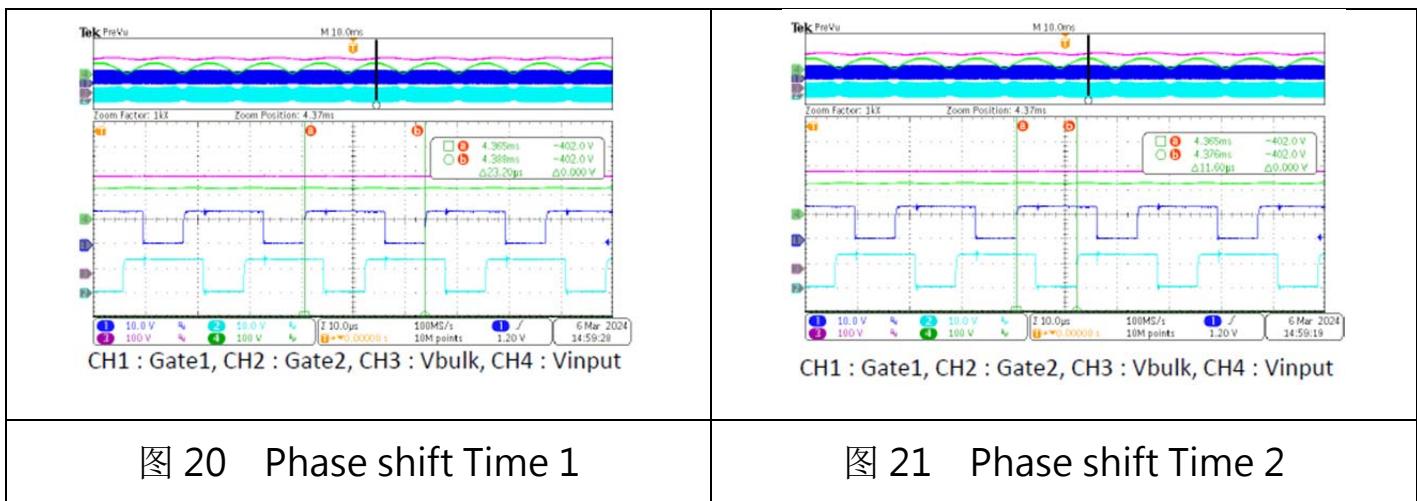

取两相 Gate 的驱动波形, 如图 1 为例, 以 Gate1 当作为基准, 计算出 Gate1 完整周期为 Time 1, 并从 Gate1 导通计时至 Gate2 导通作为 Time2, 由 Time 2 / Time 1 得到 Phase shift, 以图 20, 21, 得到 Time 1 = 23.2us, Time 2 = 11.6us, Phase shift =  $11.6\text{us} / 23.2\text{us} = 0.5 \rightarrow 0.5 * 360^\circ = 180^\circ$  相移

图 20 Phase shift Time 1

图 21 Phase shift Time 2

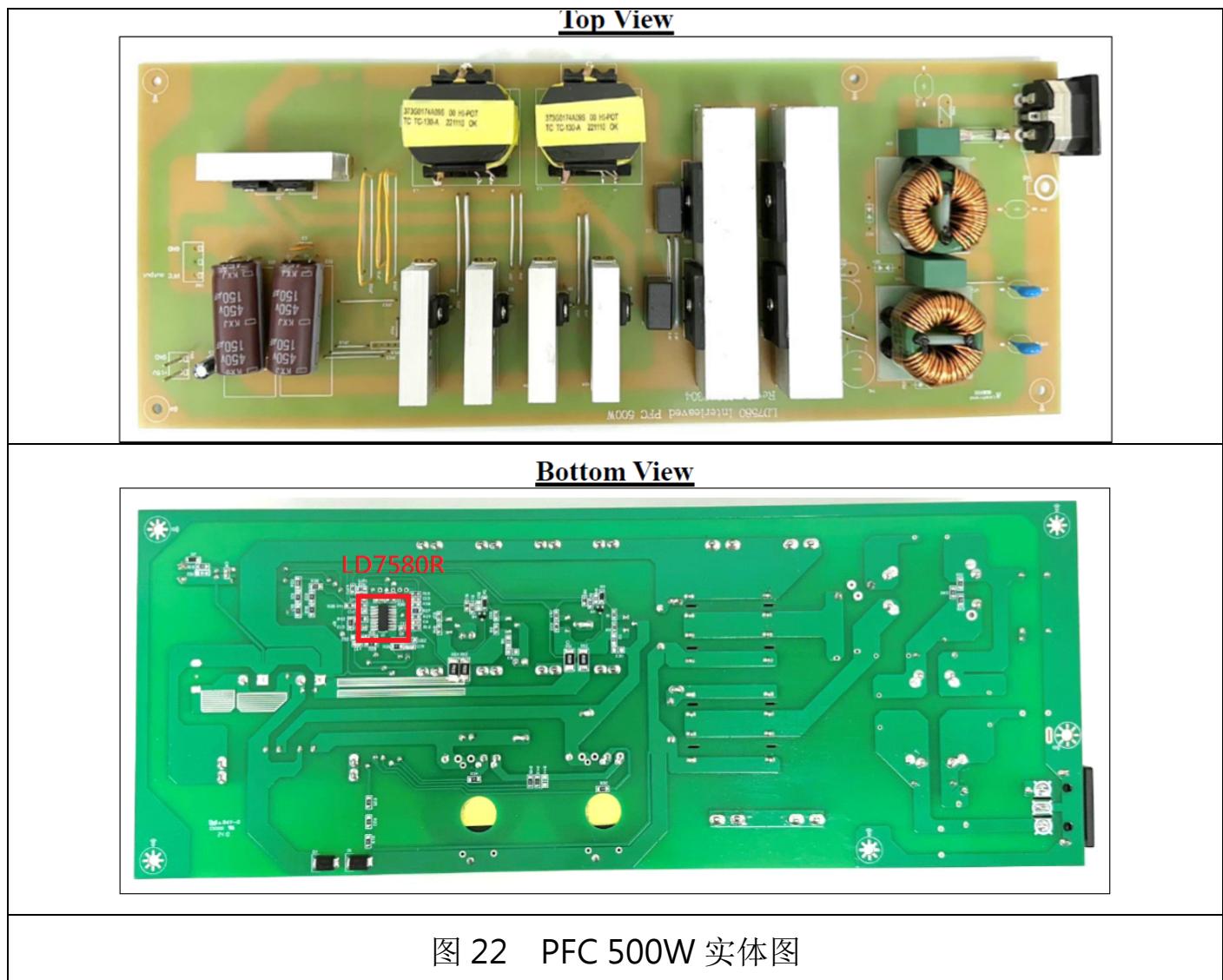

## 8 通嘉 Interleaved PFC 500W Demo Board 设计范例

Interleaved PFC : LD7580R

PCB Size: 366.5mm(L) x 142.25mm(W)

输出功率 : 390V/1.28A,

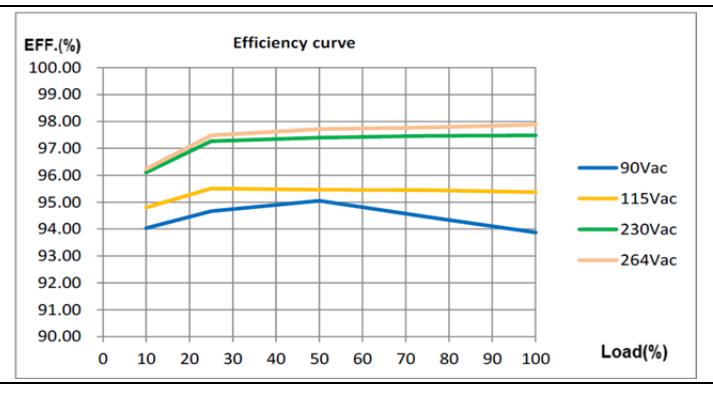

## PF 值 / 效率 / THD 测试

Test Condition :

Input : 90 ~ 264Vac

Output : 10% Load ~ 100% Load

| $V_{INAC}$<br>(V/Hz) | $V_{BUS,SET}$<br>(V) | $V_{BUS,PCB}$<br>(V) | $I_{OUT}$<br>(A) | $P_{BUS}$<br>(W) | $P_{IN}$<br>(W) | PF    | $\eta$<br>(%) | THD<br>(%) | Requirement<br>(%) |

|----------------------|----------------------|----------------------|------------------|------------------|-----------------|-------|---------------|------------|--------------------|

| 90/47                | 390                  | 392                  | 1.278            | 500.976          | 533.65          | 0.997 | 93.88         | 5.99       | > 90               |

|                      |                      | 392                  | 0.958            | 375.536          | 397.6           | 0.996 | 94.45         | 7.47       |                    |

|                      |                      | 392                  | 0.638            | 250.096          | 263.11          | 0.994 | 95.05         | 9.96       |                    |

|                      |                      | 392                  | 0.319            | 125.048          | 132.1           | 0.995 | 94.66         | 6.92       |                    |

|                      |                      | 392                  | 0.128            | 50.176           | 53.36           | 0.891 | 94.03         | 3.96       |                    |

| 115/60               | 390                  | 392                  | 1.278            | 500.976          | 525.28          | 0.996 | 95.37         | 7.17       | > 90               |

|                      |                      | 392                  | 0.958            | 375.536          | 261.99          | 0.995 | 95.46         | 5.45       |                    |

|                      |                      | 392                  | 0.638            | 250.096          | 261.99          | 0.995 | 95.46         | 6.81       |                    |

|                      |                      | 392                  | 0.319            | 125.048          | 130.93          | 0.990 | 95.51         | 3.78       |                    |

|                      |                      | 392                  | 0.128            | 50.176           | 52.93           | 0.866 | 94.80         | 6.53       |                    |

| 230/50               | 390                  | 392                  | 1.278            | 500.976          | 513.91          | 0.990 | 97.48         | 6.98       | > 90               |

|                      |                      | 392                  | 0.958            | 375.536          | 385.3           | 0.988 | 97.47         | 5.13       |                    |

|                      |                      | 392                  | 0.638            | 250.096          | 256.77          | 0.978 | 97.40         | 5.67       |                    |

|                      |                      | 392                  | 0.319            | 125.048          | 128.56          | 0.911 | 97.27         | 9.95       |                    |

|                      |                      | 392                  | 0.128            | 50.176           | 52.21           | 0.726 | 96.1          | 22         |                    |

| 264/63               | 390                  | 392                  | 1.278            | 500.976          | 511.8           | 0.984 | 97.89         | 7.26       | > 90               |

|                      |                      | 392                  | 0.958            | 375.536          | 384.07          | 0.974 | 97.78         | 8.10       |                    |

|                      |                      | 392                  | 0.638            | 250.096          | 255.94          | 0.919 | 97.72         | 9.56       |                    |

|                      |                      | 392                  | 0.319            | 125.048          | 128.28          | 0.838 | 97.48         | 17.46      |                    |

|                      |                      | 392                  | 0.128            | 50.176           | 52.14           | 0.632 | 96.23         | 33         |                    |

表四 Demo Board P.F / Eff. / THD

图 23 500W Demo Board Eff. 展示图

图 24 500W Demo Board P.F 展示图

图 25 500W Demo Board THD 展示图

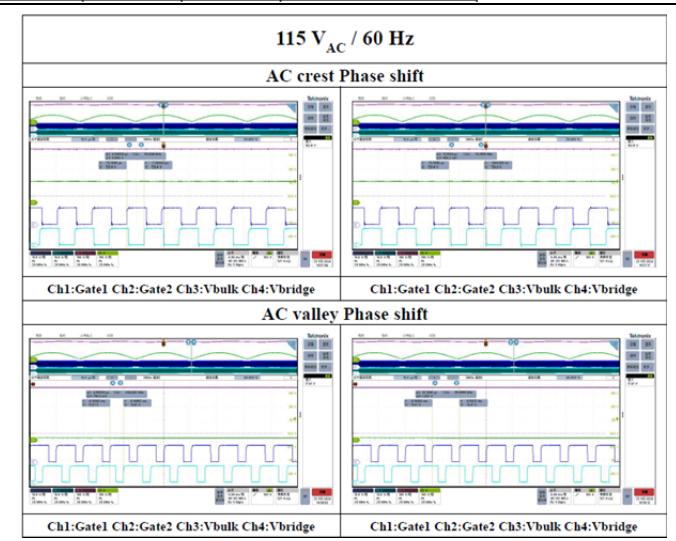

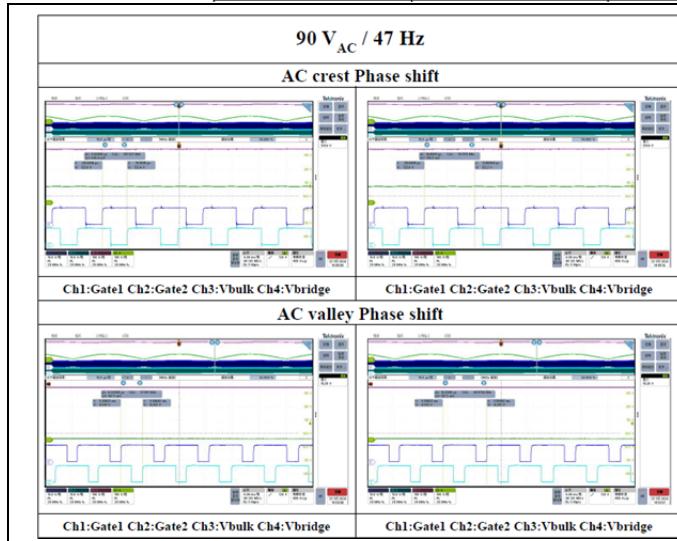

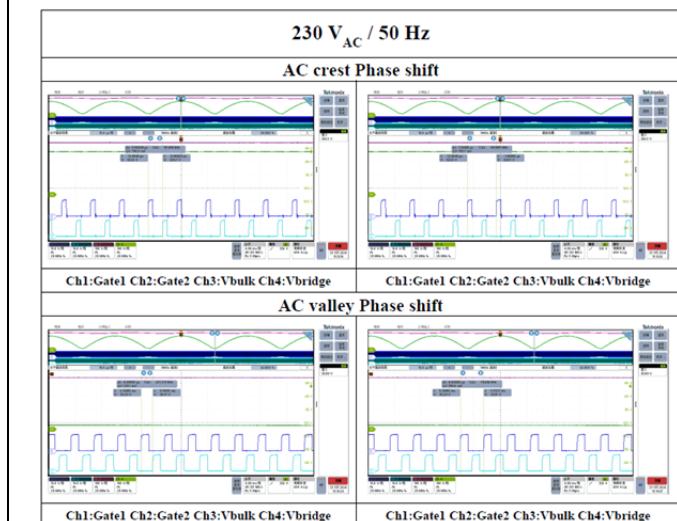

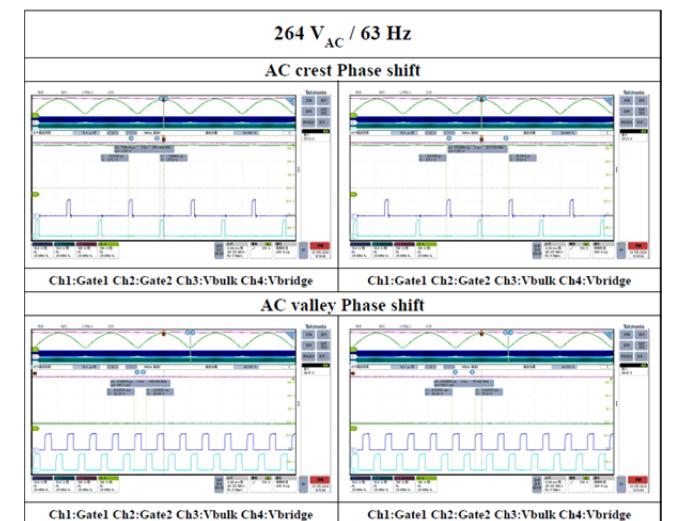

## Phase Shift 测试

|                                  |                            |                             |                             |                             |

|----------------------------------|----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Input Voltage                    | 90 V <sub>AC</sub> / 47 Hz | 115 V <sub>AC</sub> / 60 Hz | 230 V <sub>AC</sub> / 50 Hz | 264 V <sub>AC</sub> / 63 Hz |

| Output Current                   | Full Load                  |                             |                             |                             |

| Measured Point of Output Voltage | End of PCB                 |                             |                             |                             |

| Requirement                      | 45%~55% (162°~198°)        |                             |                             |                             |

| V <sub>BUS,SET</sub><br>(V) | V <sub>IN,AC</sub><br>(V / Hz) | AC crest Phase shift |       | AC Valley Phase shift |       | Requirement (%)        |

|-----------------------------|--------------------------------|----------------------|-------|-----------------------|-------|------------------------|

|                             |                                | (%)                  | (°)   | (%)                   | (°)   |                        |

| 390                         | 90 / 47                        | 49.46                | 178   | 50                    | 180   | 45%~55%<br>(162°~198°) |

|                             | 115 / 60                       | 49.61                | 178.5 | 48.51                 | 174.6 |                        |

|                             | 230 / 50                       | 50                   | 180   | 50                    | 180   |                        |

|                             | 264 / 63                       | 50                   | 180   | 50.58                 | 182   |                        |

图 26 Phase shift 90Vac

图 27 Phase shift 115Vac

图 28 Phase shift 230Vac

图 29 Phase shift 264Vac

通嘉控制器数字交错式 PFC LD7580R 能有效提升电源转换的效率和功率因子，这不仅是技术上的卓越，更是对环境永续发展的积极贡献，直接体现了节能减碳的效益。同时，它显着降低电流涟波，这不仅有助于缩小电路体积和降低成本（尤其在高功率应用中），进一步优化资源利用、减少碳足迹，呼应企业在 ESG (环境、社会与公司治理) 中环境 (E) 面向的承诺。

透过数字控制的弹性，LD7580R 能实现复杂的控制算法和全面的保护功能，从而提升电源系统的整体性能、可靠性与智能化程度。这些特性强化了电源系统的稳定性和安全性，不仅符合严格的产业标准，也为客户的永续运营提供了坚实基础，展现了良好的公司治理 (G) 与社会责任 (S)。

这种技术使得电源供应器能够更好地应对不断提高的效率要求、更严格的法规限制（特别是全球日益收紧的能源效率与碳排放标准，助力客户达成其节能减碳目标）以及日益复杂的应用需求。它是现代高性能、高功率密度电源设计的重要发展趋势，亦是企业在追求技术创新的同时，积极落实 ESG 策略的关键环节。通嘉科技在市场上受到客户的认可，并有大量量产经验，我们将提供最详细的信息及应用说明给您，同时请支持老牌 AC-DC 通嘉产品联系方式如下

通嘉 FAE 张孝泽

E-mail: [Easonchang@leadtrend.com.tw](mailto:Easonchang@leadtrend.com.tw)